Accueil Grenoble Relais Transmissions numériques TVA Links Montages Datasheet

Le projet etait en cours depuis un certain temps mais s'est acceleré aprés la question d'un amateur Italien sur le forum TVA, et les essais de M0DTS qui a montré que l'on pouvait faire de l'emission DATV en LIVE avec un PC et une solution hardware minimale. En fait cette solution prometteuse ne m'a pas interessé car les essais de M0DTS montrent qu'il faut un PC bête de course pour arriver à sortir un SR convenable (autour de 1500 avec un quadruple core ???). Ce qui confirme les discutions theoriques que j'avais suivit jusque là, le PC n'etant pas l'outil ideal pour traiter l'encodage DVB car prenant beaucoup de ressources.

Nous avons donc continué notre chemin avec plus d'ardeur, considerant que nos choix d'origines etaient les bons: encodage video possible par un PC et DVB par une carte à FPGA. Il restait donc a montrer la faisabilité et à realiser un proto.

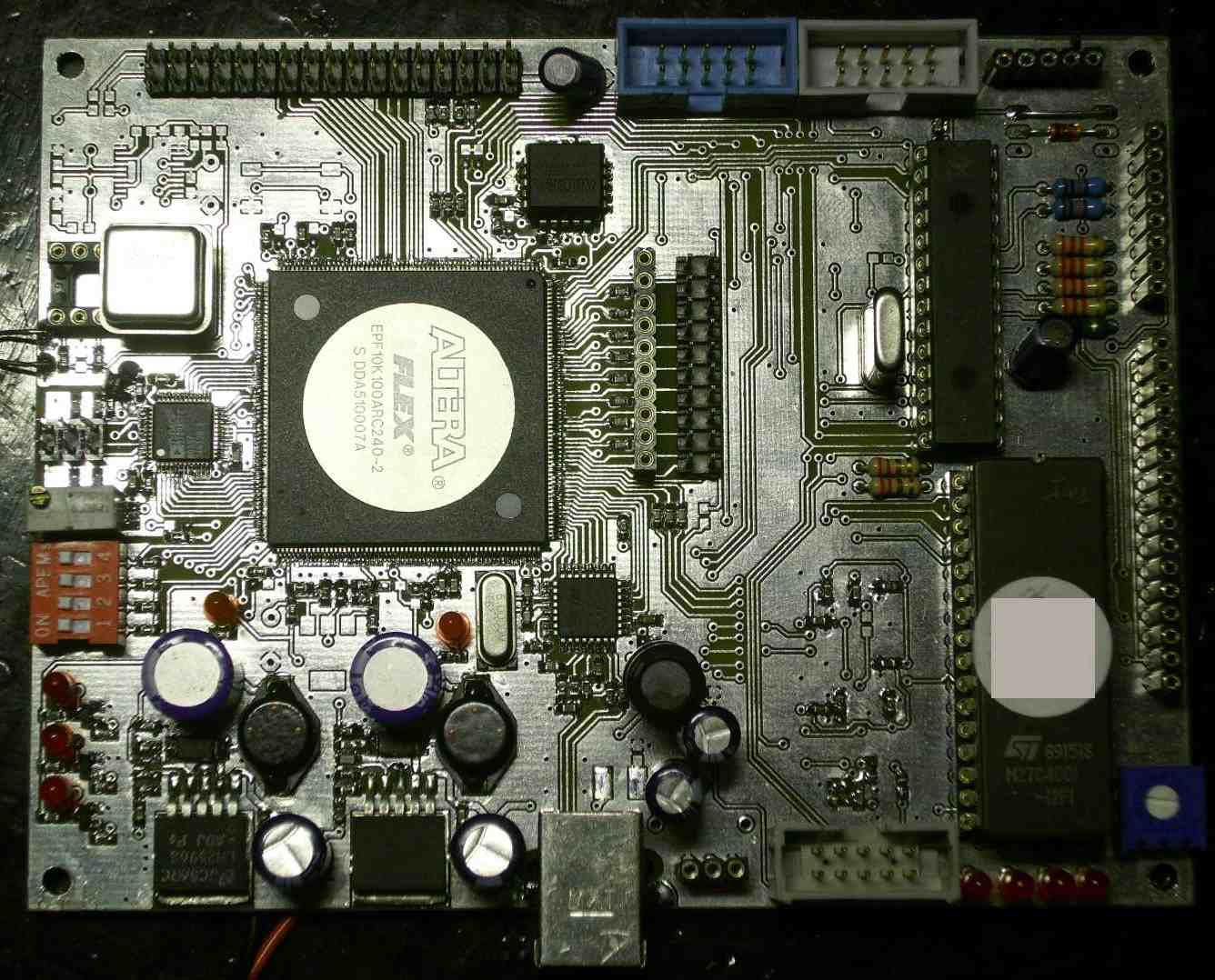

Fort de l'experience deja acquise lors de nos precedents prototypes,

j'ai donc entrepris le routage d'une carte electronique avec une grande

ambition. Implantation d'un plus gros FPGA, mais d'une ancienne generation

car recupéré dans la poubelle. Donc le montage ne sera pas

reproductible mais les resultats pourront etre utilisés pour eventuellement

un projet plus aboutit. Le defi se situe autant dans la realisation hardware,

la carte faisant appel à une majorité de CMS 0603 ainsi que

des CI au pas de 0,5mm. Il va sans dire qu'il faut du materiel pour parvenir

au but, mais rien d'insurmontable pour des amateurs motivés. La

partie software elle aussi est un defi. Code assembleur pour les fonctions

du PIC, VHDL pour le FPGA et le CPLD, deux circuits presents sur la carte.

Synoptique fonctionnel de la carte encoder2

Simulation avec le routeur de circuit imprimé

Photographie de la carte cablée

Premiers essais avec la mire à EPROM.

Dabord, la premiere etape a été la mise au point et verification

des differents etages:

- Alimentation SMPS 5V et 3,3V qui permettent l'alimentation des modules

avec le meilleur rendement.

- FPGA et un design en VHDL

- FlashRAM: c'est la premiere fois que je mettais en oeuvre un tel

composant....

- Microcontrolleur PIC 16F876

- CPLD de configuration , design VHDL.

- Les liaisons series pour la PLL a partir du µP PIC

L'EPROM sur la photo ne sera pas utilisée dans un premier temps.

Apres quelques problemes (cela faisait un certain temps que je n'avais plus fait de VHDL), un design assez simple est au point. Il ne s'agit que d'un filtre digital précédé d'un serialiser pour le lecteur HDD et un MUX pour selectionner la mire type F5SFU à liaison IQ.

Conclusion:

Les premiers essais sont concluant, une image apparait a l'ecran le

27/07/2009......

Nous voila avec le meme resultat que avec notre precedente maquette,

mais avec un puissance de calcul superieure puisque nous disposons d'un

FPGA bien plus performant. Cela nous ouvre de nombreuse perspectives.

Le prochaine etape sera la liaison USB.

Essais de transmission via port USB

C'est la premiere fois que je tente une realisation avec un port USB. C'etait donc l'inconnue.

Une description a attiré mon attention, il s'agit des essais de M0DTS. Cet OM a réalisé une transmission DATV avec comme source un PC qui transmettait un stream via un port USB. Nous savions qu'il y avait des essais en court mais le probleme semblait etre la limite du taux de transfert irregulier du aux interruptions du systeme d'exploitation Windows. L'originalité et l'idée de M0DTS est d'inserer une memoire FIFO aprés l'interface USB faite a partir d'un circuit FTDI assez connu des electroniciens et relativement facile à approvisionner. Le point delicat est le fait que ce circuit est CMS, il faut donc du materiel particulier pour le souder, c'est à dire une bonne loupe et un fer a souder à panne fine, donc rien d'insurmontable.

Les descriptions de M0DTS sont visibles sur son site internet à cette adresse:

Source de stream a partir du PC: http://www.m0dts.co.uk/datv_new.htm

Emission DATV Live a partir d'un PC: http://www.m0dts.co.uk/datv_live.htm

Tout cela est prometteur. De notre coté la premiere etape est donc d'obtenir une image a partir du PC.

Il fallait donc adapter la carte encodeur 2 pour accepter un stream via USB. Donc, montage des deux circuits CMS FT245 et IDT72221 (FTDI USB et FIFO RAM). Bien entendu, le circuit imprimé concu au printemps prevoyait le montage de ces deux circuits.

Il fallait egalement revoir le logiciel u PIC pour pouvoir selectionner l'entrée USB ainsi qu'un nouveau design pour traiter les signaux des nouveaux circuits. M0DTS a traité cela avec des circuit logiques classiques mais l'horloge est pilotée par un quartz 4MHz. En fait la cadence est de 400KHz. Mon idée est de rendre cette horloge plus rapide pour permettre un transfert USB plus rapide egalement. Le quartz du FPGA est de 40MHz, la spec du FTDI donne une frequence maxi de 10MHz.

Le premier design fut un echec !!!!!! En fait , il y avait quelque

chose (un detail !!!) que je n'ai pas compris. Perte de temps de 1 semaine

! Le deuxieme design VHDL fonctionne apparemment bien puisque les essais

ont été concluant et que nous avons obtenu les images ci

dessous....

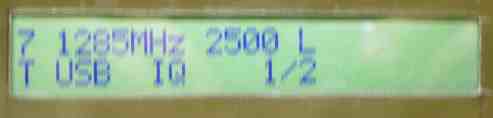

le schema de l'interface de commande FTDI et FIFO obtenu sous quartus

Exemple d'affichage sur le LCD

memoire N°7, frequence, SR type de stream et FEC

les modules pour les essais

en haut le modulateur QPSK, a gauche la carte encodeur 2 à FPGA

Voici donc les images vu sur mon moniteur, lors des essais. Le logiciel

utilisé est "usbtx" de M0DTS que je remercie ici. Car ecrire un

logiciel comme celui là m'aurait pris un certains temps, vu que

je ne suis pas un specialiste du langage C !!!

Caracteristique de la transmission:

Freq=1285MHz, SR2500, FEC=1/2

.

.

le stream mis en ligne par M0DTS

le stream de F5SBV que j'avais sur mon disque dur

un petit film aquarium , non ce n'est pas l'economiseur d'ecran de

Windows

Conclusion:

J'ai obtenu mes premieres images DATV à partir du PC et le port USB le 21/09/2009.

Les essais sont trés motivant. Avec ce systeme, on economise le tranfert de fichier vers le lecteur à disque dur. Cela fait une manipulation en moins. L'inconvenient est qu'il faut toujours avoir un PC dedié à l'emission DATV.

L'utilisation de la carte FPGA nous fait profiter de la puissance de calcul. Il y aura toujous une limite bien sur, mais pour l'instant il s'agit plus de nos conaissances limitées en programmation VHDL qui sont pénalisantes....

A suivre ......

La suite, le 14 Janvier 2010

Essais de transmission DATV LIVE

C'est la suite des essais et des efforts pour réaliser une transmission DATV, mais maintenant essayer de faire du LIVE.

Donc, état des lieux:

- je dispose d'un emetteur QPSK

- je dispose d'une interface à FPGA.

- je dispose d'une liaison PC vers USB qui me permet d'envoyer des

bouts de film depuis le PC.

Donc l'idée qui arrive ensuite, c'est de recuperer l'image d'une

source video temps reel et de la diriger vers le port USB. Comment faire

? Et bien en utilisant VLC, comme l'a deja fait M0DTS. La suite ,

voir la page datv_live1 .

Accueil Grenoble Relais Transmissions numériques TVA Links Montages Datasheet