Accueil Grenoble Relais Transmissions numériques TVA Links Montages Datasheet

Rappel des blocs mis en oeuvre dans mon premier emetteur DATV à base de mire F5SFU

F5SFU pattern generator: mire a base d'EPROM et CPLD

IQ filter: filtre analogique a base de composants L et

C.

QPSK modulator: a base d'une carte de recup d'un modulateur

GSM.

OL: PLL 2.4GHz a base de MC145151.

Les resultats ont été trés moyens, les modules employés n'etant pas forcement optimum pour l'application envisagée.

Status des projets en cours:

- QPSK modulator :

A base de AD8346, inspiré de la datasheet de Analog

Device et du montage de F1HPR.

=> Objectif: obtenir un modulateur capable de fonctionner sur 400MHz,

1200MHz et 2400MHz

=> Status: fonctionnel.

- OL :

PLL à base de circuit LMX2330 et VCO à MAX2630

MAX2653.

=> Objectif: OL bibande couvrant de 1240 à 1300MHz , 2300-2450MHz

ou 437MHz en fonction du cablage de la carte (2/3).

=> status: fonctionnel.

- IQ filter: bloc N°2 :

Filtre analogique à base de composants L C et ampli

OP à remplacer par un filtre digital basé sur la technologie

FPGA/CPLD.

=> Objectif: remplacer le filtre analogique qui est à regler par un system digital prereglé.

Filtre analogique => fonctionnel

(delicat à regler)

=> Filtre digital =>

status: premiere version fonctionnelle, améliorations en cours.

- Pattern generator: bloc N°1:

Mire F5SFU fonctionne, moulinette pour aider à la creation

du fichier IQ.

=> status: fonctionnel.

attention bug trouvé !!!!

Amelioration : design du CPLD pour lire n'importe quel

type de fichier IQ.

=> status: organigramme, VHDL en cours d'ecriture.

=> status: une solution achevée avec software pour creer une

EPROM qui fonctionne à tous les coups !

- Realisation du systeme de lecture à base de disque dur (mis au point par F1GFF/F4FAU)

=> Objectif: Posseder une systeme capable de lire un petit film (la mire lire un film de 1 seconde rebouclé sur lui meme).

=> status: fonctionnel. (trouvé un probleme sur notre premiere maquette)

Compatibilité avec le filtre FIR (Bloc N°2).

Modification pour choix du SR (1000 1667 2500) grace aux

CPLD.

=> status: en cours d'essais.... (ok SR=1000 SR=1667, test viterbi

et SR=2500 à faire)

Filtre FIR au cours des essais

Essais du 30/05/2008 (00h30!!!) systeme lecteur à disque dur conception F1GFF/F1FAU

Aprés pas mal d'essais et un rendez vous raté (le systeme

n'ayant pas pu etre mis au point pour le salon Iseramat mais fut quand

meme presenté), ce soir pour la premiere fois j'ai eu une image

sur mon ecran !!!! Champagne !!!!

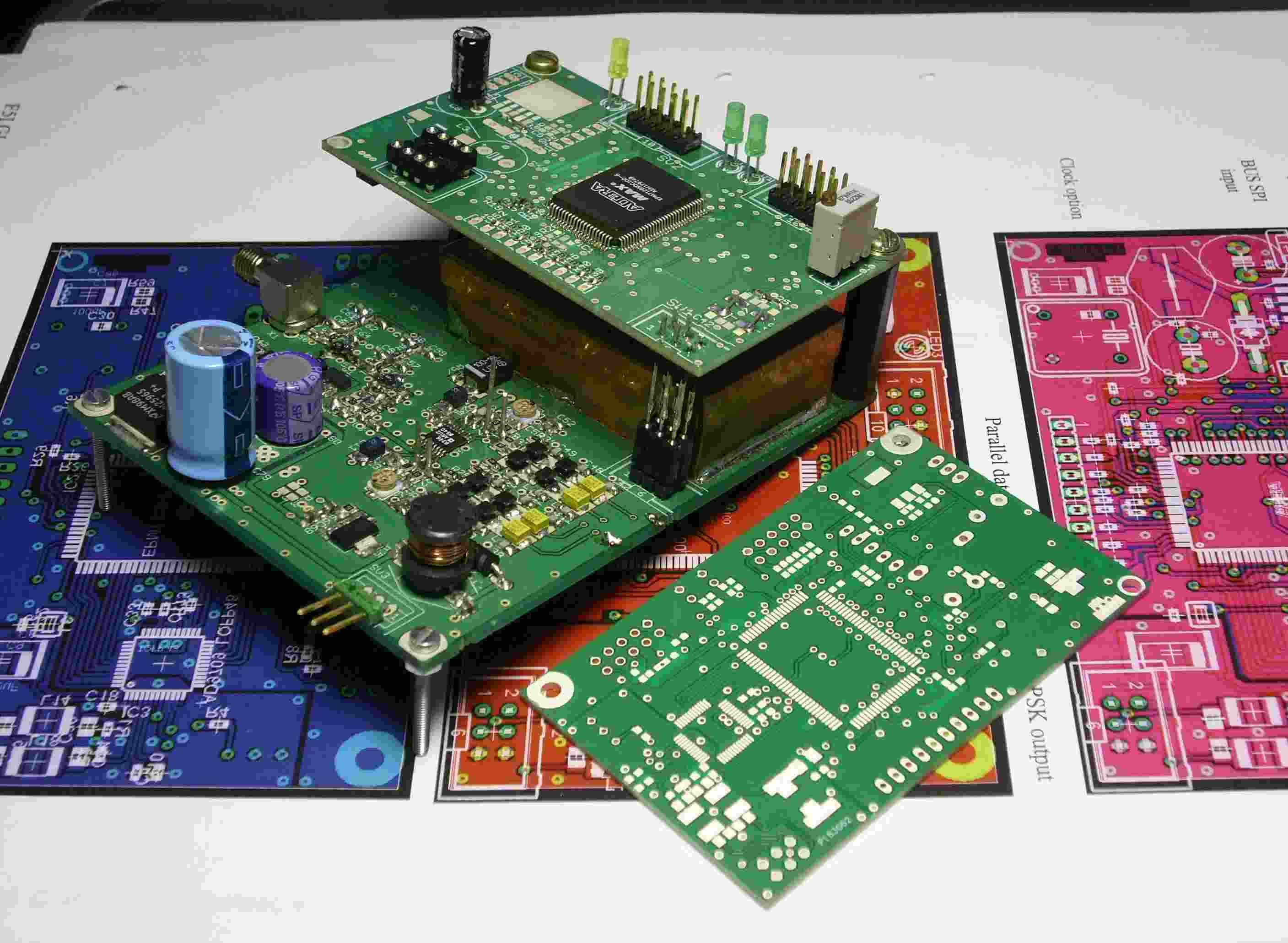

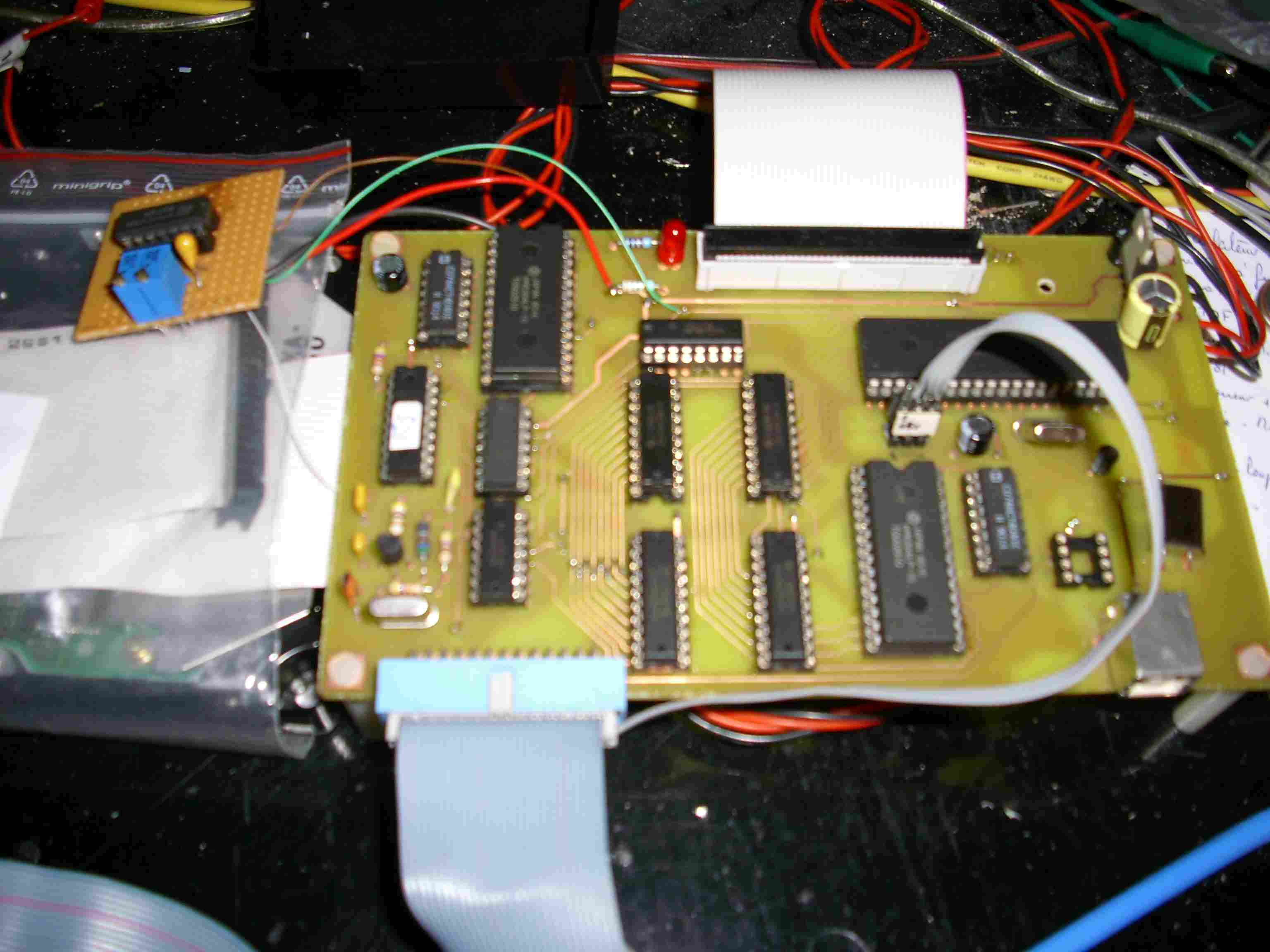

Tout d'abord, la raison du retard: il a été necessaire de rajouter une modification (carte additionnelle à gauche visible sur l'image ci dessous) afin de resoudre un probleme electronique de commande de circuit integré (commande des memoires) . Ce probleme empechait la bonne lecture et retransmission du signal DATV. Il m'a fallu quand meme 3 semaines pour debugguer ce probleme (grrrr) ........

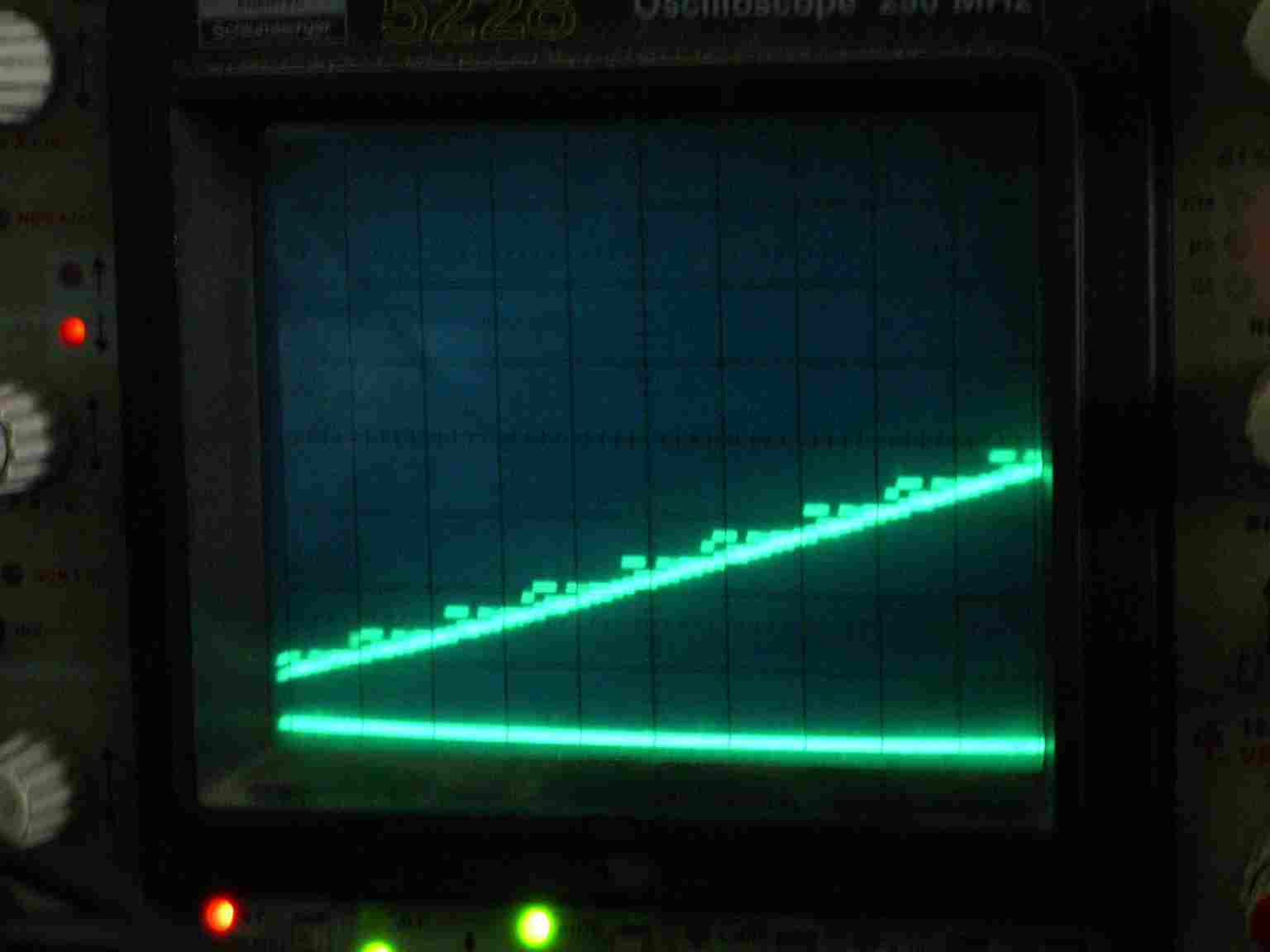

A gauche , le test du signal de rampe montre le defaut quand on regarde en etendant la base de temps de l'oscilloscope. A droite , le montage en cours de test avec la carte additionnelle. Aprés la modif, la rampe est parfaitement identique au fichier "rampe" créé et envoyé.

.

.

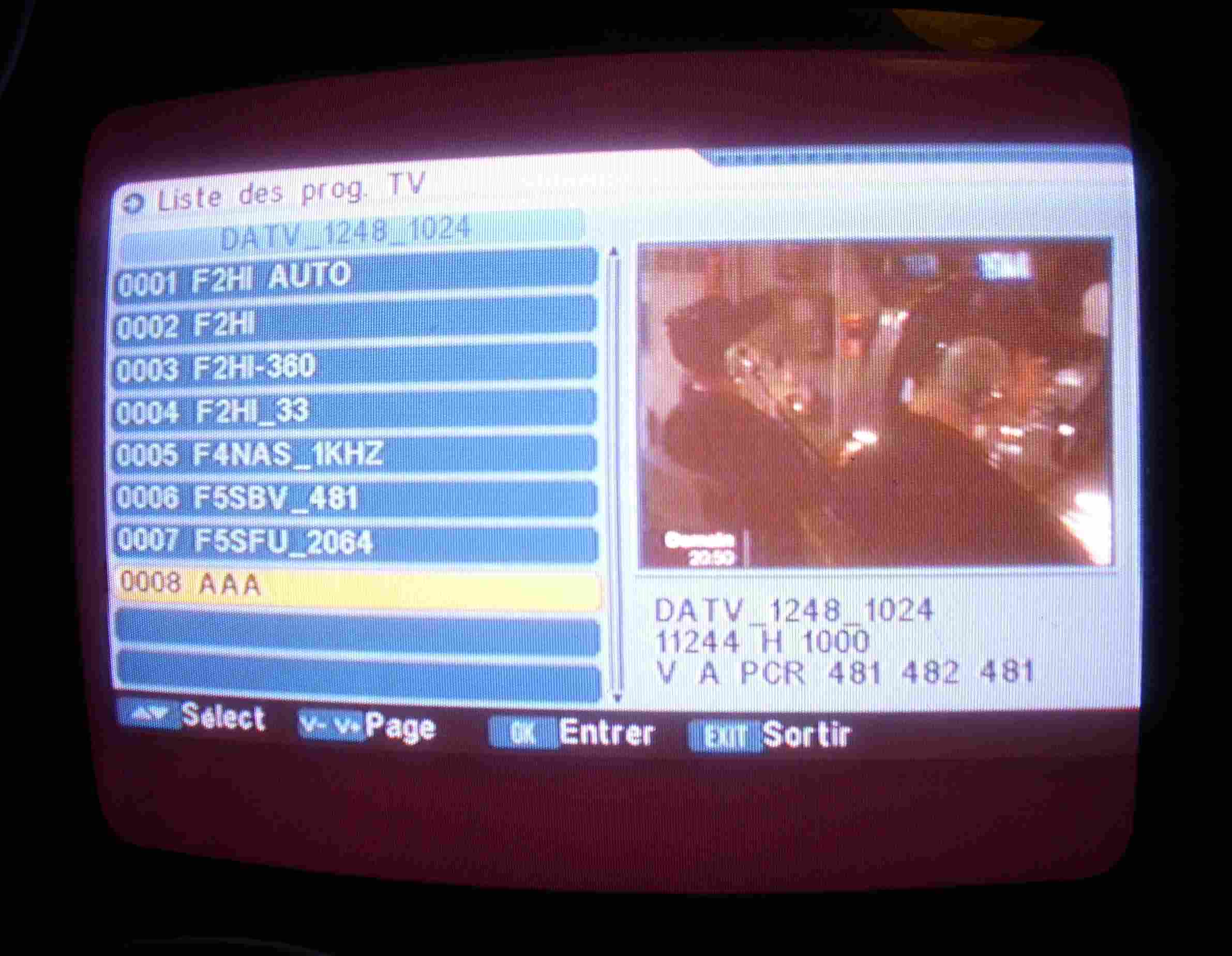

Ci dessous , l'ecran lors des premiers essais (SR=1000) et la table de manip !!!!

.

.

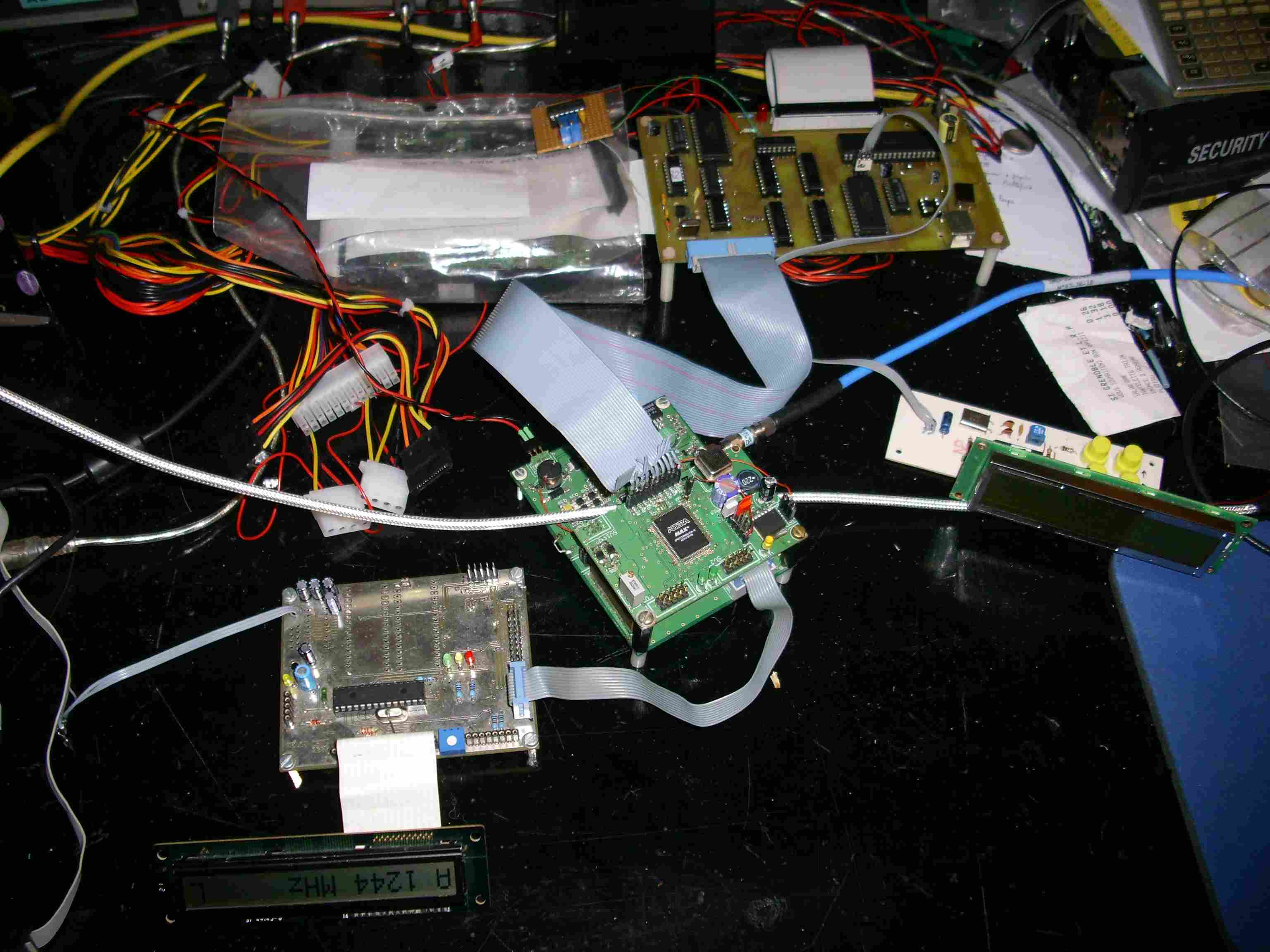

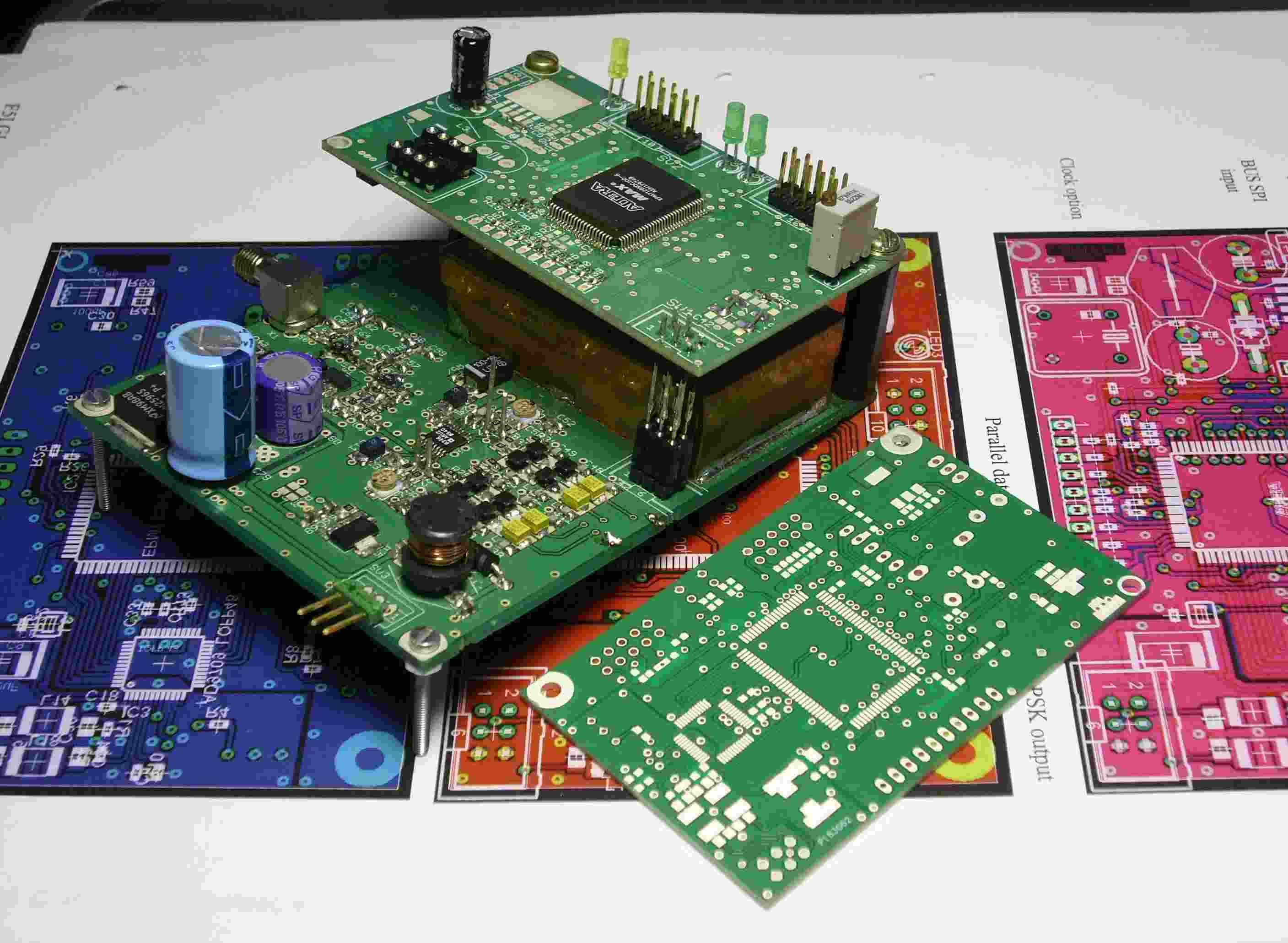

Le systeme est constitué du lecteur à disque dur qui est connecté au systeme filtre FIR à CPLD (EPM7128) en photo ci dessus. L'emetteur est constitué d'un modulateur QPSK à AD8346 et d'un PLL bi-bande à LMX2330 (ici choix 437 ou 1240/1300MHz). Les essais ont été fait uniquement en 23cm sans PA et en local avec un SR=1000.

L'interet du systeme à CPLD est de pouvoir changer de SR. Des essais avec un SR de 1667 sont prevus, et peut etre plus (2500) si le disque dur arrive à suivre.....

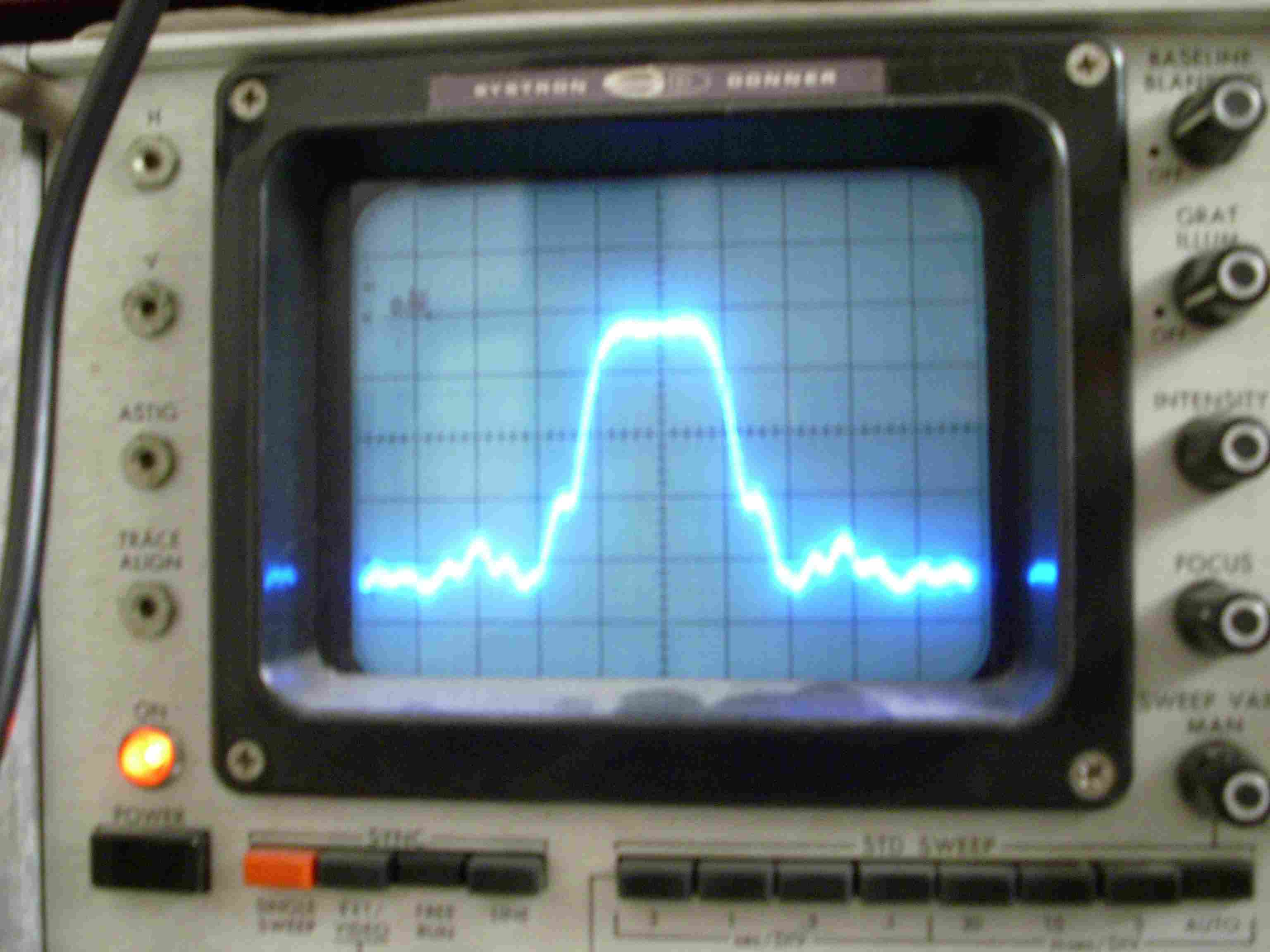

Voir le spectre ci dessous obtenu avec le FIR du CPLD:

Il y a encore un peu d'ajustage à faire pour gagner sur l'ACPR,

c'est a dire rejeter à un niveau non visible les deux epaules.

Le 06 juin 2008, essais avec SR=1667 directement: ca marche, j'ai du avoir de la chance avec un disque dur rapide !

Essais en prevision, avec un SR=2500. A suivre...

Description du system d'interfacage à CPLD (FIR9):

Ci dessous la photo de la carte modulateur QPSK et synthetiseur (dessous)

ainsi que le filtre FIR et interface d'entrée (dessus):

Ci dessous le synoptique du systeme:

Premier bloc:

- interfacage des signaux d'entrée (serialiseur et convertisseur

viterbi).

- filtre FIR.

- bloc diviseur pour calcul des horloges.

Deuxieme bloc:

- bloc diviseur pour calcul des horloges correspondants aux SR (1000,

1667 et 2500 en prevision).

- interpolateur pour sur echantillonnage des datas (amelioration du

spectre)

Dernier bloc:

- convertisseur digital/analogique 8bits AD9709.

Conclusion sur les essais du lecteur HDD

Fonctionnel avec SR=1000, 1666 et 2500 en mode

viterbi

Tous les disques durs ne fonctionnent pas

avec ce systeme.

- Une maquette fonctionne bien.

- Une autre maquette pose des problemes.

On estime que les probleme viennent des deux

cartes electroniques:

- HDD: disques dur pas tous performants

pour la fonction.

difficulté de reproduction en fonction des composants montés

(marque des IC etc).

- carte CPLD: chauffe et donc les parametres

electroniques peuvent changer en fonction de la temperature des CPLD.

=> Conclusion: construire un encodeur avec un FPGA plus puissant.

Accueil Grenoble Relais Transmissions numériques TVA Links Montages Datasheet