http://www.dutchtronix.com/ScopeClock.htm

Accueil . Grenoble . Relais . Transmissions numériques . TVA . Links . Montages . Datasheet

INTRODUCTION

Lors de la viste de salon radiamateur, F1GE presentait en meme temps que ses oscilloscopes un montage dont la fonction nous est familière mais dont la réalisation était tres surprenante. Marcel F1GE avait realisé ce kit :

http://www.dutchtronix.com/ScopeClock.htm

Le probleme est que le signal XY ne peut pas etre utilisé comme source d'image pour une TV par exemple. De meme transporter un signal XY ou l'emettre n'est pas simple. De ce besoin a germé l'idée de créer un dispositif capable de convertir le signaux XY en video composite.

Je suis partit sur la realisation d'un plugin (terme employé

en micro informatique et peut etre pas approprié ici), c'est à

dire un montage qui s'ajouterait au kit existant. Ainsi pas de problème

de piratage, on conserve le montage complet de dutch avr mais malheureusement

le cout sera bien sur superieur..

EVALUATION

|

Voici ce que donne ce montage sur l'ecran d'un oscilloscope: L'image ne semble pas trés nette. Je pensais au depart que cela

venait de la connection des sondes qui n'était pas tres propre,

combiné aussi avec la grande bande passante de l'appareil de mesure.

Il y a peut etre aussi un probleme de jitter autant dans le montage que

dans le systeme d'affichage de l'oscilloscope.

|

|

| Comment les signaux XY sont ils fabriqués ?

J'ai donc commencé par etudier par une analyse à l'oscilloscope numerique. Une capture de datas montre comment les signaux sont élaborés. Le microcontrolleur fabrique deux vecteurs X et Y numeriques qui seront convertis en analogique par un DAC afin d'etre envoyé vers les voies X et Y d'un oscilloscope. Tout le probleme est de connaitre le protocole et les timings, chose rendu possible par cette capture. L'idée est alors d'intercepter ces datas digitales avant convertion pour les stocker dans une memoire afin de les relire sequentiellement au cadencement d'une trame video.

|

|

A partir de cette analyse, j'ai élaboré un dispositif capable de capturer les dats, les stocker, les relire au bon moment et les convertir en image video.

Ci dessous le synoptique du systeme memoire d'image. Il s'agit de toute la logique imaginée pour réaliser les fonctions necessaires au transfert des datas vers la RAM puis à la relecture ainsi que la generation des clock et synchronisations.

Voici les fonctions essentielles de ce dispositif:

1 - interception des datas en digital.

2 - effacement de la memoire avant enregistrement.

3 - rangement de ces datas dans la memoire (dans l'ordre).

4 - generation des clock ligne et trame pour synchroniser l'image.

5 - relecture de la memoire et fabrication de l'image.

Le synoptique montrant les fonctions dans le CPLD:

On pourrait faire toutes ces fonctions avec des circuits logiques

mais cela ressemblerait à une usine à gaz ! Aujourd'hui,

des circuits modernes permettent une grande integration, je veux parler

des CPLD ou FPGA. J'ai commencé par developper un design (nom moderne

donné à la conception du circuit electronique pour un FPGA)

afin d'evaluer quelle puissance de circuit etait necessaire. J'avais une

carte à disposition avec un EPM7128 de la famille MAX7000S. Apres

quelques modifications, je suis arrivé aux premiers resultats. J'ai

ensuite réalisé un proto afin de rendre le montage compact,

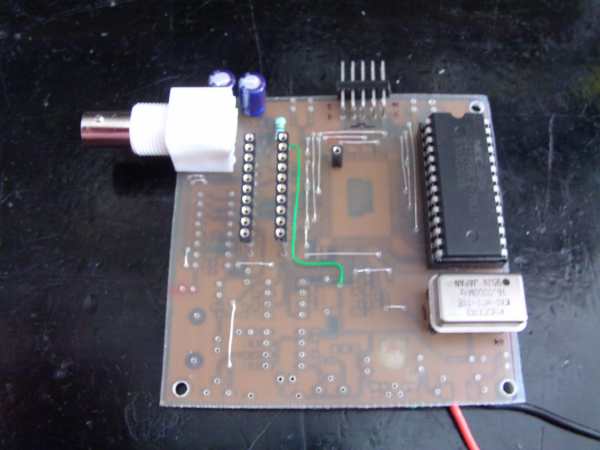

voir les diverses photos ci dessous:

|

|

| Ci dessus , la face superieure ou composants classiques. | Ci dessus, la face inferieure ou composants CMS. |

|

|

| Ci dessus deux vues du montage une fois assemblé. | La sortie video est disponible sur la BNC inferieure. |

ESSAIS et MISE AU POINT

Voici le resultat du proto en photo:

| Cette image est flatteuse car elle montre une image presque parfaite.

Mais il y a des erreurs lors du traitement des datas. Ceci reflete des problemes lors du traitement ou du transfert des datas vers la memoire qui se traduisent par des pixels allumés aux mauvais endrois. Par exemple l'heure serigraphiée n'est pas nette, il y a un point à coté du onze etc....

|

AMELIORATIONS EVISAGEES

-> diminuer la taille de l'horloge dans un coin de l'ecran avec incrustation dans une image exterieure.

Pour cela, des blocs sont necessaires comme :

- un generateur de synchronisation ligne et trame d'une image

exterieure.

Actuellement, le montage est autonome et genere lui meme

les signaux de synchronisation.

- un detecteur de presence de signal video.

Il est preferable d'avoir un tel bloc afin de commuter

en mode autonome s'il n'y a pas de signal video ou bien si la video est

noyée dans le bruit.

Ces deux blocs sont routés sur le circuit imprimé, mais

pas cablés. Un LM1881 pour la synchro, un NE567 pour la detection

du 15625Hz.

Il faut completer le design du CPLD. Par contre comme ce dernier est

plein à 95% par le design actuel, il n'est pas evident que ces ajonctions

puissent tenir dans les 5% restant.

CONCLUSION (provisoire)

Comme le resultat est moyen, mes esperances ont été un peu refroidies! Il y a trop de d'erreurs de pixel à mon gout et pour l'instant, je ne suis pas sur de continuer dans ce projet. De plus, les ameliorations envisagées ne tiendont peut etre pas dans le CPLD, d'ou un changement probable et un redesign du circuit imprimé etc...

A suivre.

Page lue

fois.

Accueil . Grenoble . Relais . Transmissions numériques . TVA . Links . Montages . Datasheet